Abstract: This paper studies a distributed environment foreign object intrusion detection system based on SOPC technology. The system integrates the acquisition, processing and transmission of video data into a single FPGA. The acquisition and processing parts are written into hardware modules in hardware description language. It is connected to the Nios II system, and the transmission part adopts the Ethernet interface IP core, and is constructed into a SOPC system to realize the foreign object intrusion monitoring system. At the same time, users can easily add IP cores to extend system functionality. Finally, verification was performed on Altera's DE2 development platform to meet the design requirements.

Keywords: programmable system-on-chip (SOPC); foreign object intrusion; video capture; Nios II

This article refers to the address: http://

With the rapid development of China's economy and society, the railway passenger and cargo transportation volume is increasing, and the train running speed is continuously increasing, which brings great pressure to the railway safety monitoring. The railway foreign body intrusion limit seriously affects the running safety of the train. Due to the unpredictable environmental factors in the open-air high-speed driving, the orbital foreign body intrusion may have serious consequences for driving safety. Orbital foreign bodies refer to obstacles on the railway that affect the safety of normal driving, such as landslides, mudslides, etc., sands on the roads, suspensions dropped by bridge tunnels, and construction workers who are still stuck on the road due to alarm errors and related equipment. . Due to the high speed, low miss detection rate and low false alarm rate of the railway foreign body intrusion detection system, the traditional software-based IDS is facing more and more pressure, and only the improvement of the pattern matching algorithm is invaded. The increase in detection speed is limited and is not the fundamental strategy for solving the problem.

SOPC (System On a Programmable Chip) is called a programmable system-on-chip. It is a flexible and efficient solution with a short design cycle and low design cost. SOPC Bu-ilder is a tool for Altera to implement the SOPC concept for building a system defined at the module and component levels. SOPC Builder's component library includes a range of components from simple fixed logic blocks to complex, parameterized, dynamically generated subsystems. Users can also easily create custom SOPC Builder components for easy implementation. Configuration of system functions. This paper presents a front-end monitoring system for foreign object intrusion in distributed train environment. By constructing Nios II soft core processor, various peripherals and custom components on FPGA, a customized SOPC real-time monitoring system is designed and implemented. Real-time acquisition and processing of front-end video data is completed, and data is transmitted to the train control center via the network.

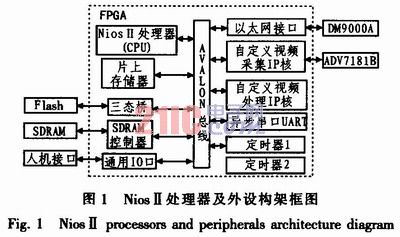

1 System overall architecture This system uses SOPC to realize the front-end monitoring function of foreign object intrusion in distributed train environment. A Nios II processor system consists of a Nios II CPU and a series of peripherals to develop an embedded system based on Nios-II. The key is how to customize Nios II and design custom interfaces according to functional needs. The system uses ADV7l8lB to complete the analog video decoding process, complete the conversion of CVBS and other analog video signals to YCrCb digital signals, and design the video data acquisition module IP core with hardware description language (VHDL) to realize the front-end video data acquisition. Since the collected video data is massive data, this brings great inconvenience to the storage and transmission. The video data needs to be preprocessed to reduce the amount of data. The system uses VHDL to design the corresponding video data processing module IP core. Finally, the data is transmitted to the train control center through the network, and the Ethernet interface module uses the Ethernet interface IP provided by Youjing Technology. Add these IP cores to the Nios-II system with the formation of custom components, and add some necessary memory, man-machine interface and timers to build the required SOPC system. The block diagram of the whole system is shown in Figure 1. Show.

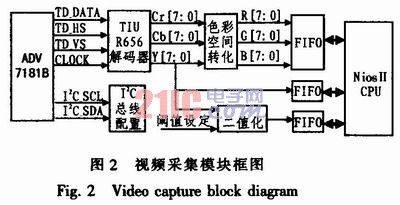

2 Video image acquisition and processing module design The acquisition module is a very important part of the whole system. The quality of the acquisition will directly affect the recognition effect of the whole system. The system video A / D converter selects ADV7181B, which can automatically detect and convert standard NTSC, PAL and SECAM analog TV baseband composite signals, and output 4:2:2 conforms to ITU-R656 (International Telecommunication Union video standard) Standard 16-bit/8-bit composite video data supporting the input of 6 analog video signals. The ADV7l81B is configured through the I2C bus and can output line and field sync signals at the same time. The digital video data output by the ADV718lB is transmitted to the FPGA via the 8-bit bus TDDATA. The FPGA recognizes the valid data in the video data through the video decoding module, and then processes the image according to the requirements of the image precision, and generates three kinds of data images, respectively RGB color image, gray image and binarized image, and finally transmits the image. Into the cache FIFO, output to the Nios II CPU. Finally, the video data is written to the SDRAM by the processor. 2 is a block diagram of a video capture processing module, in which the ratio of the data amount of the color map, the gray scale image, and the binary image is 384:128:1, and an image of a different data amount can be selected according to the needs of the actual video image.

The functions of each module in the system are briefly described as follows:

1) The ITU-R656 decoding module receives the digital video stream sent from the video A/D converter ADV7181B, and then decodes the digital video stream to generate a YUV3 video signal to identify the line and field sync signals.

2) The three video buffer module systems each design a FIFO. According to the size of the video data, the buffer depth is different, and is used for buffering video data. The FIFO is designed using the parameterizable macro function module and LPM function provided by Altera, specifically through the GUI wizard of the Mega Wizard Plug-In Manager.

3) The I2C configuration module initializes the ADV7181B through the I2C bus, and selects the generated digital video format.

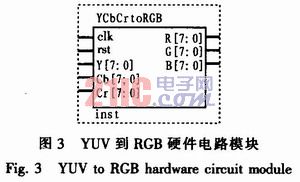

4) The color space conversion module completes the conversion of the color space from YUV to RGB, so that the video data is suitable for display in VGA. The color space is converted from YUV to RGB. The corresponding hardware description language is written according to the following conversion formula.

R=1.0Y+O+1.402 (Cr-128)

G=1.0Y-0.344 13(Cb-128)-0.714 14(V-128)

B=1. OY+1.772 (Cb-128)

The resulting YUV to RGB hardware circuit module is shown in Figure 3.

5) The output of Y in Fig. 2 is the gray value of the image, and the information of Y value can completely describe a gray image (the gray level is 256). After the gray value is binarized, a binarized image can be obtained. The key is the selection of the threshold. Here, the gray threshold is set to an adjustable input amount, and the ideal can be set according to the specific application environment. Threshold. The binarized hardware module is also described by the hardware description language. The generated module is shown in Figure 4. The working principle is to output l when the image value is greater than the threshold, otherwise output O.

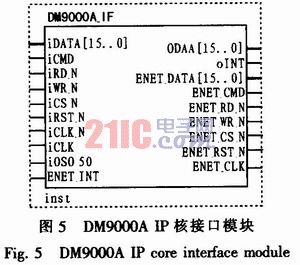

3 Video data image transmission module design The video data image transmission part uses the Ethernet interface IP core of the SOPC Builder tool, and adds it to the Nios II system to construct the SOPC system. Among them, DM9000A is a high-speed network controller with a general-purpose processor interface, a 10/100M PHY and 4K bytes of SRAM, which supports 8-bit and 16-bit data interfaces. SOPC Builder provides the interface logic required to connect the DM-9000A to the Avalon bus. Figure 5 shows the DM9000A IP core interface module, which is divided into two parts: input and output. One part is the connection signal between the module and the Avalon bus, and the other part is the signal connected between the module and the DM9000A outside the FPGA.

Finally, the NiosII soft core processor configured as needed is shown in Figure 6. NiosII is a user-configurable universal RISC embedded processor. The Nios II Integrated Development Environment (IDE) is the basic software development tool for the Nios II series of embedded processors. All software development tasks can be done under NiosIIIDE.

4 Conclusion This paper introduces a SOPC-based distributed environment foreign object intrusion front-end monitoring system, and introduces the design and configuration process of SOPC hardware system, and the software design of NiosII soft-core processor based on this hardware system configuration. Finally, it was tested on Altera's DE2 development platform, and the front-end grayscale image was monitored as shown in Figure 7, which achieved the purpose of front-end detection. The software flow of the train environment foreign body intrusion monitoring system includes the initialization of each module and the flow control of each module, mainly including video acquisition control, image processing control, image SDRAM storage control, Ethernet interface control flow and so on.

The innovation based on SOPC technology design is that not only software can be programmed, but also the hardware system is programmable. This provides great convenience for flexible configuration of the system and flexible design of the software, and is also beneficial to the later optimization of the system. And upgrades. When designing, pay attention to whether hardware implementation or software simulation is selected according to the specific hardware resource size and implementation speed requirements. At the same time, pay attention to the anti-jitter design of the front-end acquisition module. This tailored hardware configuration method can maximize the cost performance of the system, making SOPC technology have a wide application space in the environmental foreign body intrusion monitoring system. The HardCopy technology can also be used to convert the distributed environment foreign object intrusion detection system implemented on the FPGA device directly to the ASIC through a specific technology.

Digital Desk Clock,Digital Clock For Desk,Table Digital Clock,Movie Clapper Digital Clock

Guangzhou Huanyu Clocking Technologies Co., Ltd. , http://www.findclock.com